|

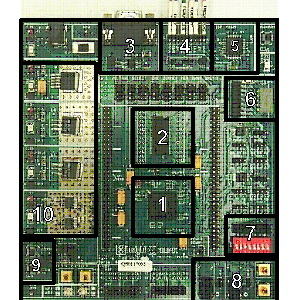

1: Xilinx Virtex-II (XC2V1000) 2: Micron 256Mb DDR SDRAM (4Mb Ѓ~ 16Ѓ~ 4banks) 3: RS-232 interface 4: JTAG interface 5: XC18V04 ISP PROM 6: 7-segment LED display 7: User DIP switches 8: Clock source (100MHz / 24MHz / User clock) 9: User push buttons 10: Voltage regulators (3.3V / 2.5V / 1.8V / 1.5V) |

|||

| Block Diagram of LEON Processor | FPGA BOARD by Insight Electronics | |||

|

Los Angeles - UCLA |

||||